专利详情

专利详情

- 专利名称:

- 发明

三维存储装置、系统及其形成方法

- 申请公布号:

- CN117673035A

- 申请公布日:

- 2024-03-08

- 申请号:

- 2022110828588

- 申请日:

- 2022-09-06

- 申请人:

- 长江存储科技有限责任公司,

- 地址:

- 430000 湖北省武汉市东湖新技术开发区未来三路88号

- 发明人:

- 谢景涛,颜丙杰,张坤,周文犀,夏志良,霍宗亮,

- 分类号:

- H01L23/538(2006.01);H10B43/20(2023.01);H10B43/30(2023.01);H10B43/40(2023.01);H10B41/20(2023.01);H10B41/30(2023.01);H10B41/40(2023.01);H01L21/768(2006.01);

- 专利代理机构:

- 北京永新同创知识产权代理有限公司 11376

- 代理人:

- 林锦辉

- 最终专利权人:

- 摘要:

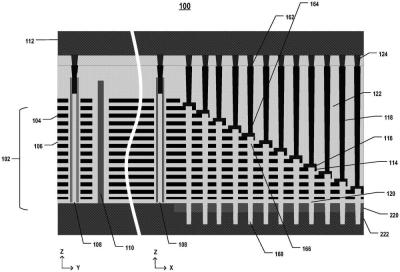

- 公开了一种三维(3D)存储装置,其包括堆叠体、多个接触结构和多个支撑结构。绝缘结构中的堆叠体包括交替堆叠的导电层和电介质层,并且堆叠体包括阶梯结构。每个接触结构延伸穿过绝缘结构并且与阶梯结构中的相应导电层接触。支撑结构延伸穿过阶梯结构中的堆叠体。接触结构布置成第一行和第二行,接触结构的第一行与外围装置电接触,并且接触结构的第二行与外围装置电绝缘。

- 权利要求书:

- 1.一种三维(3D)存储装置,包括:堆叠体,所述堆叠体包括交替堆叠的多个导电层和多个电介质层,其中,所述堆叠体包括阶梯结构;在所述堆叠体和所述阶梯结构之上的绝缘结构;多个接触结构,所述多个接触结构中的每个接触结构延伸穿过所述绝缘结构并且与所述阶梯结构中的所述多个导电层中的相应导电层接触;以及多个支撑结构,所述多个支撑结构延伸穿过所述阶梯结构中的所述堆叠体,其中,所述多个接触结构沿第一方向布置成第一行和第二行,所述第一行与所述第二行相邻且平行,所述多个接触结构的所述第一行与外围装置电接触,并且所述多个接触结构的所述第二行与所述外围装置电绝缘。2.根据权利要求1所述的3D存储装置,其中,所述多个接触结构中的每个接触结构还包括与所述多个导电层中的所述相应导电层接触的阶梯触点。3.根据权利要求2所述的3D存储装置,其中,所述阶梯触点设置在所述多个接触结构与所述多个支撑结构之间。4.根据权利要求1‑3中任一项所述的3D存储装置,其中,所述多个接触结构和所述多个支撑结构在所述3D存储装置的平面图中重叠。5.根据权利要求4所述的3D存储装置,其中,所述多个支撑结构中的每个支撑结构与所述多个接触结构中的一个接触结构对准。6.根据权利要求1‑5中任一项所述的3D存储装置,其中,所述多个接触结构和所述多个支撑结构包括不同的材料。7.根据权利要求1‑6中任一项所述的3D存储装置,其中,所述多个支撑结构包括电介质材料。8.根据权利要求1‑7中任一项所述的3D存储装置,其中,所述多个接触结构包括导电材料。9.根据权利要求1所述的3D存储装置,还包括:在所述堆叠体之下的半导体层;以及延伸穿过所述堆叠体并与所述半导体层接触的沟道结构,其中,所述多个支撑结构延伸至所述半导体层。10.根据权利要求9所述的3D存储装置,其中,所述半导体层和所述多个接触结构被所述多个导电层中的至少一个导电层分开。11.根据权利要求3所述的3D存储装置,其中,所述多个接触结构中的每个接触结构包括远离所述阶梯触点的第一端和靠近所述阶梯触点的第二端,并且所述第一端的宽度大于所述第二端的宽度。12.根据权利要求11所述的3D存储装置,其中,所述多个支撑结构中的每个支撑结构包括靠近所述阶梯触点的第三端和远离所述阶梯触点的第四端,并且所述第三端的宽度大于所述第四端的宽度。13.根据权利要求12所述的3D存储装置,其中,所述第一端的宽度大于所述第三端的宽度。14.一种系统,包括:被配置为存储数据的三维(3D)存储装置,所述3D存储装置包括:绝缘结构中的堆叠体,所述堆叠体包括交替堆叠的多个导电层和多个电介质层,其中,所述堆叠体包括阶梯结构;多个接触结构,所述多个接触结构中的每个接触结构延伸穿过所述绝缘结构并且与所述阶梯结构中的所述多个导电层中的相应导电层接触;多个支撑结构,所述多个支撑结构延伸穿过所述阶梯结构中的所述堆叠体;以及存储控制器,所述存储控制器耦合到所述3D存储装置并被配置为控制所述3D存储装置的操作,其中,所述多个接触结构沿第一方向布置成第一行和第二行,所述第一行与所述第二行相邻且平行,所述多个接触结构的所述第一行与外围装置电接触,并且所述多个接触结构的所述第二行与所述外围装置电绝缘。15.一种用于形成三维(3D)存储装置的方法,包括:形成电介质堆叠体,所述电介质堆叠体包括交替堆叠的多个第一电介质层和多个第二电介质层;在所述电介质堆叠体处形成暴露所述多个第一电介质层的一部分的阶梯结构;在所述阶梯结构之上形成绝缘结构;形成穿透所述电介质堆叠体和所述绝缘结构的多个开口,其中,所述多个开口中的每个开口包括位于所述开口内部的阻挡结构;在所述多个开口中、在所述阻挡结构上方形成多个接触结构;在所述多个开口中、在所述阻挡结构下方形成多个支撑结构;以及用多条字线替换所述多个第一电介质层。16.根据权利要求15所述的方法,其中,在所述电介质堆叠体处形成暴露所述多个第一电介质层的所述部分的所述阶梯结构包括:去除所述电介质堆叠体的一部分以形成暴露所述多个第一电介质层的所述阶梯结构,其中,所述电介质堆叠体的外部区域处的每两个相邻的第一电介质层在水平方向上偏移一距离。17.根据权利要求15或16所述的方法,其中,形成穿透所述电介质堆叠体和所述绝缘结构的所述多个开口包括:在所述电介质堆叠体的外部区域处的每个第一电介质层上形成半导体层;以及形成穿透所述半导体层的所述多个开口。18.根据权利要求17所述的方法,其中,在每个第一电介质层上形成所述半导体层包括:在所述电介质堆叠体的所述外部区域处的每个第一电介质层上形成多晶硅层。19.根据权利要求17所述的方法,还包括:在由所述多个开口暴露的所述半导体层上形成所述阻挡结构。20.根据权利要求19所述的方法,其中,在由所述多个开口暴露的所述半导体层上形成所述阻挡结构包括:执行选择性外延生长(SEG)操作以在由所述多个开口暴露的所述半导体层上形成所述阻挡结构。21.根据权利要求19所述的方法,其中,在由所述多个开口暴露的所述半导体层上形成所述阻挡结构包括:在由所述多个开口暴露的所述半导体层上执行氧化操作,以在由所述多个开口暴露的所述半导体层上形成所述阻挡结构。22.根据权利要求12‑18中任一项所述的方法,其中,在所述多个开口中在所述阻挡结构下方形成所述多个支撑结构包括:在所述多个开口中形成第三电介质层;以及去除所述第三电介质层的一部分以暴露牺牲结构的底部。23.根据权利要求22所述的方法,其中,用所述多条字线替换所述多个第一电介质层包括:去除所述牺牲结构以在所述电介质堆叠体中形成缝隙开口;通过所述缝隙开口去除所述多个第一电介质层、所述阻挡结构和所述半导体层以形成多个空腔;以及在所述多个空腔中形成所述多条字线。24.根据权利要求23所述的方法,其中,所述多个第一电介质层和所述阻挡结构在不同操作中被去除。25.根据权利要求15‑24中任一项所述的方法,还包括:将外围装置键合在电介质堆叠体上、与所述多个接触结构的一部分接触。26.一种用于形成三维(3D)存储装置的方法,包括:形成电介质堆叠体,所述电介质堆叠体包括交替堆叠的多个第一电介质层和多个第二电介质层;在所述电介质堆叠体处形成暴露所述多个第一电介质层的一部分的阶梯结构;在所述阶梯结构之上形成绝缘结构;形成穿透所述电介质堆叠体和所述绝缘结构的多个开口,其中,穿透所述电介质堆叠体和所述绝缘结构的所述多个开口在一次光刻操作中形成;在所述多个开口中的每个开口内部形成阻挡结构;在所述多个开口中、在所述阻挡结构上方形成多个接触结构;在所述多个开口中、在所述阻挡结构下方形成多个支撑结构;以及用多条字线替换所述多个第一电介质层。

| 日期 | 最新法律状态 | 描述 |

|---|---|---|

| 2024-03-26 | 实质审查的生效 | 实质审查的生效 IPC(主分类):H01L23/538 专利申请号:2022110828588 申请日:20220906 |

| 2024-03-08 | 公开 | 公开 |

安徽飞镖知识产权服务股份有限公司

皖ICP备18021682号-1